The browser version you are using is not recommended for this site.

Please consider upgrading to the latest version of your browser by clicking one of the following links.

- Safari

- Chrome

- Edge

- Firefox

Article ID: 000074796

Content Type: Error Messages

Last Reviewed: 10/19/2022

Error (14703): Invalid internal configuration mode for design with memory initialization

Environment

Bug ID: 466229; 2205637334

Version Found: 17.1

You may see this error while compiling a custom FIFO or a RAM block in the Intel® Quartus® Prime Software Standard or Lite versions for an Intel® MAX® 10 device.

This error is seen because Intel® MAX® 10 device compact variants do not support memory initialization. If you have not provided any mif file for your custom design and still see this error in Intel® Quartus®Prime Edition Software, it may be because a mif file is being inferred by the RTL coding style

Signal declaration for memory_type should be changed from

signal mem : memory_type :=(others => (others => ‘0’));

to

signal mem : memory_type;

This is to ensure that memory is not initialized and there is no compilation error in the Assembler stage.

- Description

- Resolution

Need more help?

Give Feedback

Disclaimer

Another question was open, it seems a duplicate but:

I restarted design of another board where exhibiting strange defect. Prepared a a fresh new project file, I reloaded all IP core and connected on QSYS, then I generated a ROM linked to HEX file, all seems good and project get the right way…

Correcting connection bug and parameter where mistyped,all seems good.

Relese another bug on forgot clock enable and LE usage grown from 2600LE to 5800LE .. init error return again and don’ go away from!!

Don’t go away removing files, removing rom and flash IP.

Don’t go away cleaning project, rebuilding Qsys.

DOn’t go away erasing ….

Cannot erase my job my time, reputation.

I start thinking quartus became a big crap, just try’d again oldest version and again same error.

Return to 18.1 clean project, no way to clean error.

QUARTUS is at this time unusable on MAX10, timing error reported on code it work, synthesis is wrong for sure.

Again Network module exhibit some strange issues, respond to ARP messages and do nothing other, at first compile probing from internal EThernet RX was dead.

Reversed RX and TX just to see if it where an hardware error on board, started working.

Appeared RX signal on internal route but It work? No reply just ARP.

To do so means it decode packet but after that?

Ip core was debugged and working.

Timing error where reported from internal PLL clock output?? How can I fix them?

Routed clock to external pin seems they where ok no jitter exact frequency….

LCD controller doesn’t work properly. Image is stable but seems not initialized, I discovered processor was stopped…

Released no way to compile with rom in Qsys…

No way to recompile code, I think increased code consumed space, switched from sc08 to SC25, same scenario.

Removed rom, init files, still assembler refuse to compile.

New assembly has also new error on same code of previous project .

So I decided ask again google and I found this scaring thread:

https://forums.intel.com/s/question/0D50P00003yyRM5SAM/max10-flash-memory-specifications

Describe in exact word same pain I am suffering from when I started using MAX 10….

Datasheet are unclear and confusing and software tool is too much unreliable to use these device in a production. I have to suffer again to presentation, I feel the desire to change FPGA provider.

I got a low cost Lattice stick to do a test: code work as is.

I don’ t own recent xilinx device, I provide an arrangement with fae on Monday to test my code on that platform.

Flow Status Assembler Failed — Fri May 24 16:36:07 2019

Quartus Prime Version 18.1.0 Build 625 09/12/2018 SJ Lite Edition

Revision Name Top

Top-level Entity Name top

Family MAX 10

Device 10M08SCE144C8G

Timing Models Final

Total logic elements 6,150 / 8,064 ( 76 % )

Total registers 2513

Total pins 95 / 101 ( 94 % )

Total virtual pins 0

Total memory bits 173,376 / 387,072 ( 45 % )

Embedded Multiplier 9-bit elements 0 / 48 ( 0 % )

Total PLLs 1 / 1 ( 100 % )

UFM blocks 1 / 1 ( 100 % )

ADC blocks 0

Error (14703): Invalid internal configuration mode for design with memory initialization

Error (14703): Invalid internal configuration mode for design with memory initialization

Error (14703): Invalid internal configuration mode for design with memory initialization

Error (14703): Invalid internal configuration mode for design with memory initialization

Error: Quartus Prime Assembler was unsuccessful. 16 errors, 1 warning

Error: Peak virtual memory: 840 megabytes

Error: Processing ended: Fri May 24 16:36:07 2019

Error: Elapsed time: 00:00:02

Error: Total CPU time (on all processors): 00:00:02

Error (293001): Quartus Prime Full Compilation was unsuccessful. 18 errors, 295 warnings

10M25SCE144C8G

Error (14703): Invalid internal configuration mode for design with memory initialization

Error (14703): Invalid internal configuration mode for design with memory initialization

Error (14703): Invalid internal configuration mode for design with memory initialization

Error: Quartus Prime Assembler was unsuccessful. 16 errors, 1 warning

Error: Peak virtual memory: 852 megabytes

Error: Processing ended: Fri May 24 16:29:23 2019

Error: Elapsed time: 00:00:02

Error: Total CPU time (on all processors): 00:00:03

Error (14703): Invalid internal configuration mode for design with memory initialization

Это потому что,

Режим конфигурации неверно

Изменился на следующее

Интеллектуальная рекомендация

указатель-события: нет; решить проблему сбоя клика

На работе сделал выпадающий список. Фон стрелки вниз добавляется к form-select :: after, но при нажатии стрелки событие раскрывающегося списка не может быть запущено. Так что добавьтеpointer-events: n…

Как идея соединяет MySQL?

1. Открытая идея 2. Справа есть база данных, щелкните 3. Нажмите » +» 4. Продолжайте нажимать 5. Выберите MySQL 6. Введите, где находится база данных, имя пользователя, пароль, тестовое соед…

CSRF и SSRF

Введение в уязвимости CSRF CSRF (подделка межсайтовых запросов, подделка межсайтовых запросов) относится к использованию недействительной идентификационной информации жертвы (файлы cookie, сеансы и т….

Разработка управления приложениями

Получить всю информацию о приложении PackageManager Android управляет пакетами приложений через PackageManager, и мы можем использовать его для получения информации о приложениях на текущем устройстве…

Вам также может понравиться

Анализ исходного кода пула потоков -jdk1.8

openjdk адрес загрузки http://hg.openjdk.java.net/jdk8u/jdk8u/jdk/tags Логические шаги пула потоков, с которыми поставляется Java, — это, в основном, следующие шаги: Реализация псевдокода Отправить ис…

Используйте инструменты в макете XML:

В макете, если некоторые фиксированные значения атрибута не установлены, некоторое представление не будет видно, когда будет видна макет. Все, что мы можем увидеть эффект предварительного просмотра, к…

Войдите в JVM

1. Введение в JVM 1.1 Концепция JVM Введение в виртуальную машину: JVM (аббревиатура от Java Virtual Machine. Java Virtual Machine.), JVM — это настраиваемый компьютер, которого на самом деле не сущес…

пользователи Linux и группы пользователей

Пользователь категория Профиль пользователь Root (Root пользователя) Команда Советы Упорядочить #, имеет самую высокую задачу разрешения любого разрешения файла недействительно для корневого пользоват…

Котлин Базовый — класс и атрибуты

Давайте напишем простой JavaBean класса Student в Java, только с одним свойством, имя. Тот же класс в Котлин это: PUBLIC в Котлин является видимость по умолчанию, поэтому его можно опустить. Этот вид …

Статьи по теме

- MAX10

- Оракул логина разработчика PlSql появляется ошибка инициализации

- Ошибка памяти появляется при установке TensorFlow на ubuntu16.04

- [*Linux*] -linux Установка JDK1.8 Появляется ошибка во время инициализации виртуальной машины

- Ошибка CUDA: во время проверки pytorch появляется нехватка памяти

- Потребление памяти Gitlab большое, и 502 решения по ошибкам часто появляются

- Ошибка COBALTSTRIKE 4.0 произошла во время инициализации решения памяти библиотеки агента виртуальной машины Решение об увеличении/ошибке решения

- У Win10 есть ошибка, которая появляется в подготовленном VPN -соединении -L2TP Попытка подключения не удалась, потому что уровень безопасности столкнулся с ошибкой обработки при инициализации и удаленном компьютерном переговоре

- Решение использования JUNIT появляется инициализация.

- Max10 Debug NIOS Notes Notes

популярные статьи

- Кордова копировать плагин Кордова-плагин-буфер обмена

- О дизайне Android и его значении

- Режим программных компонентов

- npm

- Vue Mobile Phone Picture Component Component

- 0,96-дюймовый OLED-дисплей Изображение

- Информация о контенте автоматически развернута, а мышь останавливается

- Концепция Spring и система анализа псевдонимов исходного кода (2)

- Re -Learning Record от входа в тюрьму [7]

- Камень-ножницы для бумаги (машинный тест)

рекомендованная статья

- Данные сайта веб-сайта бизнес-аналитика Python Reptile

- KVM виртуальная машина примечания конфигурации

- 2020-07-27 Комиксы Упаковка и скачать CRAC

- В Windows, Maven частные службы Nexus строительства и эксплуатации

- Разделение чтения-записи конфигурации Springboot (Mybatis)

- Работа шесть

- Luogu p3238 [hnoi2014] дорожная блокировка

- Установка системы Windows System —- Windows7 Enterprise Edition Невозможно установить Net.framework4.52-4.6 Версия Win7 Solutions …

- Fiber Optic Cable vs Wireless: Which One Would You Prefer

- Stateful Future Transformation

Связанные теги

- Pytorch

- linux

- Java

- CobaltStrike

- jvm

- java

- tomcat

- сервер

- Опыт обмена

- junit

Topic: Need help with Altera NIOS II processors. (Read 3507 times)

0 Members and 1 Guest are viewing this topic.

Hello,

I’ve been hopelessly trying to implement NIOS II processor in my de10-lite FPGA board and I haven’t succeeded thus far. I tried various tutorials and tried different versions of quartus, but somehow I didn’t get it right. I get the following error:

Error (11176): Alt_sld_fab.: version not allowed for EModuleProperty (full version of this attached)

I asked this in Altera’s forum and I didn’t get any help. There are a few similar threads in Altera’s forum they all seem dead with no solution to this problem.

Has anyone had any experience with NIOS 2 processors? Anyone encountered this problem before?

Logged

Which version of Quartus are you using? Can you share the whole project? (you can create an archive from the project menu)

Logged

The following users thanked this post: palpurul

I think .qar file is what you are asking for. I am using quartus 16.0, but I used 18.0 as well. No change.

I attached the .qar file to my reply.

Logged

Well this is strange. I imported your archive in my version of Quartus (16.1) and didn’t run into your problem. I had another error instead:

Error (14703): Invalid internal configuration mode for design with memory initialization

I’m not familliar with the Max10 so I don’t know what exactly is Quartus’ deal with memory initialization but just for the test I disabled the memory initialization in the on_chip_memory_0 component in Qsys, regenerated and recompiled, and this time it went all the way through without any error.

Could it be a problem with your Quartus installation? Can you try and reinstall it?

Do you have a license for the Nios II processor? If not, when selecting the Nios II/f it will generate a time limited compiled image that needs to stay connected to the USB blaster to work, and maybe this part is triggering a bug in Quartus Try selecting the Nios II/e core instead and check if this changes anything. The Nios II/e core doesn’t require any extra license. Don’t forget to regenerate in QSys before you recompile your project in Quartus.

Logged

Well this is strange. I imported your archive in my version of Quartus (16.1) and didn’t run into your problem. I had another error instead:

Error (14703): Invalid internal configuration mode for design with memory initialization

I’m not familliar with the Max10 so I don’t know what exactly is Quartus’ deal with memory initialization but just for the test I disabled the memory initialization in the on_chip_memory_0 component in Qsys, regenerated and recompiled, and this time it went all the way through without any error.

Could it be a problem with your Quartus installation? Can you try and reinstall it?

Do you have a license for the Nios II processor? If not, when selecting the Nios II/f it will generate a time limited compiled image that needs to stay connected to the USB blaster to work, and maybe this part is triggering a bug in Quartus Try selecting the Nios II/e core instead and check if this changes anything. The Nios II/e core doesn’t require any extra license. Don’t forget to regenerate in QSys before you recompile your project in Quartus.

I am using the free version. I tried NIOS 2/e and I get the same error. I didn’t know NIOS 2/f requires paid licence in some cases. I better stay away from it. I follow 2 different tutorial on how to implement NIOS 2 and I followed it step by step nothing worked. strangely, they use the same version of quartus and they don’t have any license. Just wierd.

I tried 2 different versions of quartus nothing really changes, tried reinstall a few times nothing changed. Should I try 15.0 also. Is there any «least painful» version of quartus?

Logged

You can use the Nios II/f without license, but it generates additional logic to enable the «opencore plus evaluation mode», where your design needs to be connected permanently to a USB blaster, or the CPU will stop. As your error message seemed to be related to a JTAG module I thought this could be the issue.

As for the version, I find all versions of Quartus equally painful

Logged

The following users thanked this post: palpurul

You can use the Nios II/f without license, but it generates additional logic to enable the «opencore plus evaluation mode», where your design needs to be connected permanently to a USB blaster, or the CPU will stop. As your error message seemed to be related to a JTAG module I thought this could be the issue.

As for the version, I find all versions of Quartus equally painful. Do you have sample projects with your kit that you could try and compile?

«equally painful» that’s a nice way yo put it. I hate the time when I start to use a new development tool to start programming something. They are almost always very difficult to start.

I tried different examples from Altera desing stores for my development board. They have bunch of different examples involving NIOS II, but none of them compiled. Some of them gave me differen errors some of them gave me the same errors.

Not sure what’s going on and Altera won’t help me

What should I try next? different vendor?

Logged

I’ll try it in a different computer when I got home. Let’s hope that it compiles this time.

Logged

Are you using SignalTap logic analyzer as well?

Logged

Are you using SignalTap logic analyzer as well?

I think I’m not. Not really sure.

How do I check this?

Logged

I’ll try it in a different computer when I got home. Let’s hope that it compiles this time.

Not suprisingly, no change.

Logged

Are you using SignalTap logic analyzer as well?

I think I’m not. Not really sure.

How do I check this?

If you didn’t create a signaltap project and include it (it’s a *.stp file) in your FPGA project then the answer is no. You can always check in the assignment > settings > SignalTap II Logic Analyzer window.

It wasn’t used in the project archive you sent.

I was actually wondering that too, especially since your error message seems to come from somewhere around a virtual JTAG module, but I think it is actually the OpenCore evaluation module for the Nios II/f. That’s why I hoped that switching to the license free Nios II/e would help.

Logged

Are you using SignalTap logic analyzer as well?

I think I’m not. Not really sure.

How do I check this?If you didn’t create a signaltap project and include it (it’s a *.stp file) in your FPGA project then the answer is no. You can always check in the assignment > settings > SignalTap II Logic Analyzer window.

It wasn’t used in the project archive you sent.I was actually wondering that too, especially since your error message seems to come from somewhere around a virtual JTAG module, but I think it is actually the OpenCore evaluation module for the Nios II/f. That’s why I hoped that switching to the license free Nios II/e would help.

Nothing really worked so far. I am waiting for Altera support to help me. I update when the problem is solved.

Thanks for your help!

Logged

Skip to main content

Welcome to EDAboard.com

Welcome to our site! EDAboard.com is an international Electronics Discussion Forum focused on EDA software, circuits, schematics, books, theory, papers, asic, pld, 8051, DSP, Network, RF, Analog Design, PCB, Service Manuals… and a whole lot more! To participate you need to register. Registration is free. Click here to register now.

-

Digital Design and Embedded Programming

-

PLD, SPLD, GAL, CPLD, FPGA Design

You should upgrade or use an alternative browser.

run paralel some NIOS cores

-

Thread starternguyentk

-

Start dateApr 30, 2016

- Status

- Not open for further replies.

-

#1

- Joined

- Apr 30, 2016

- Messages

- 2

- Helped

- 0

- Reputation

-

0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

-

25

I am new member.

Help me, please!

I have a problem and need your helps.

I want to build two NIOS-qsystem and run two independent softwares on them.

But have an error when I try to build hardware program.

Error «14703 Invalid internal configuration mode for design whith memory initialization»

Anyone else has met this problem.?? and how can I resolve this error??

( I have two Nios-Systems: amax10_qsys.qsys and my_qsys.qsys

In top-leval verilog file I cal two these Nios-Systems:

Code dot - [expand]

when I compile the program, this error occur:

Error «14703 Invalid internal configuration mode for design whith memory initialization»

how can I resolve this error??

Help me!

Last edited by a moderator: Apr 30, 2016

-

#2

-

#3

- Joined

- Apr 30, 2016

- Messages

- 2

- Helped

- 0

- Reputation

-

0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

-

25

Typically when you have an error like this, use a search engine and search for the error first.Google returns the link below as the first one using this search string «14703 Invalid internal configuration mode for design with memory initialization«

https://www.altera.com/support/support-resources/knowledge-base/solutions/rd10302014_959.htmlIt says to add the following line to the qsf file «set_global_assignment -name ENABLE_ERAM_PRELOAD ON» as a workaround.

Thank for your helps!

I added assignment «set_global_assignment -name ENABLE_ERAM_PRELOAD ON» to qsf file but not work

after that I change Configuration Mode to «Single uncompressed image with Memory Initialization», and it work for me

To change Configuration Mode, go to

Assignments -> Device -> Device and Pin Options -> Configuration -> Configuration Mode: Single uncompressed image with Memory Initialization

- Status

- Not open for further replies.

-

Digital Design and Embedded Programming

-

PLD, SPLD, GAL, CPLD, FPGA Design

-

This site uses cookies to help personalise content, tailor your experience and to keep you logged in if you register.

By continuing to use this site, you are consenting to our use of cookies.

Содержание

- Error 39022 found no valid memory initialization file to process

- Update memory initialization file in Quartus project for remote system update

- Error 39022 found no valid memory initialization file to process

- Update memory initialization file in Quartus project for remote system update

- Error 39022 found no valid memory initialization file to process

- Update memory initialization file in Quartus project for remote system update

- Русские Блоги

- MAX10 появляется ошибка инициализации памяти

- Интеллектуальная рекомендация

- Реализация оценки приложения iOS

- JS функциональное программирование (е)

- PWN_JarvisOJ_Level1

- Установка и развертывание Kubernetes

- На стороне многопроцессорного сервера — (2) *

- Вам также может понравиться

- C#Личные заметки

- [Springcould] Код сервисного шлюза (Zuul)

- Решите проблему, что координаты и значения данных с несколькими скидками для echarts не совпадают

- Список () и кортеж () Методы в Python

- HP ProLiant DL360 Gen9 — Memory initialization error

- Дубль два

Error 39022 found no valid memory initialization file to process

Success! Subscription added.

Success! Subscription removed.

Sorry, you must verify to complete this action. Please click the verification link in your email. You may re-send via your profile.

- Intel Communities

- Product Support Forums

- FPGA

- Intel® Quartus® Prime Software

- Re: Re:Update memory initialization file in Quartus pr.

Update memory initialization file in Quartus project for remote system update

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have implemented remote update on cyclone IV FPGA board. After the power cycle the factory image is configured and then the nios boots correctly. When I configure the application image without the application hex file, the sof is configured properly. I checked it by using PIO in Qsys and assigning different values to the fpga pins. In the factory configuration the fpga pin has 3 volts and in the application image it has 0 volts. I was also able to download elf file on the application image from eclipse.

Источник

Error 39022 found no valid memory initialization file to process

Готово! Подписка добавлена.

Готово! Подписка удалена.

Извините, вы должны пройти верификацию для завершения этого действия. Нажмите ссылку верификации в своем электронном сообщении. Вы можете повторить отправку через свой профиль.

- Intel Communities

- Product Support Forums

- FPGA

- Intel® Quartus® Prime Software

- Update memory initialization file in Quartus project for remote system update

Update memory initialization file in Quartus project for remote system update

- Подписка на RSS-канал

- Отметить тему как новую

- Отметить тему как прочитанную

- Выполнить отслеживание данной Тема для текущего пользователя

- Закладка

- Подписаться

- Отключить

- Страница в формате печати

- Отметить как новое

- Закладка

- Подписаться

- Отключить

- Подписка на RSS-канал

- Выделить

- Печать

- Сообщить о недопустимом содержимом

I have implemented remote update on cyclone IV FPGA board. After the power cycle the factory image is configured and then the nios boots correctly. When I configure the application image without the application hex file, the sof is configured properly. I checked it by using PIO in Qsys and assigning different values to the fpga pins. In the factory configuration the fpga pin has 3 volts and in the application image it has 0 volts. I was also able to download elf file on the application image from eclipse.

Источник

Error 39022 found no valid memory initialization file to process

Success! Subscription added.

Success! Subscription removed.

Sorry, you must verify to complete this action. Please click the verification link in your email. You may re-send via your profile.

- Intel Communities

- Product Support Forums

- FPGA

- Intel® Quartus® Prime Software

- Re: Re:Update memory initialization file in Quartus pr.

Update memory initialization file in Quartus project for remote system update

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

I have implemented remote update on cyclone IV FPGA board. After the power cycle the factory image is configured and then the nios boots correctly. When I configure the application image without the application hex file, the sof is configured properly. I checked it by using PIO in Qsys and assigning different values to the fpga pins. In the factory configuration the fpga pin has 3 volts and in the application image it has 0 volts. I was also able to download elf file on the application image from eclipse.

Источник

Русские Блоги

MAX10 появляется ошибка инициализации памяти

Error (14703): Invalid internal configuration mode for design with memory initialization

Режим конфигурации неверно

Изменился на следующее

Интеллектуальная рекомендация

Реализация оценки приложения iOS

Есть два способа получить оценку приложения: перейти в App Store для оценки и оценка в приложении. 1. Перейдите в App Store, чтобы оценить ps: appid можно запросить в iTunes Connect 2. Встроенная оцен.

JS функциональное программирование (е)

Давайте рассмотрим простой пример, чтобы проиллюстрировать, как используется Reduce. Первый параметр Reduce — это то, что мы принимаем массив arrayOfNums, а второй параметр — функцию. Эта функция прин.

PWN_JarvisOJ_Level1

Nc первый Затем мы смотрим на декомпиляцию ida Перед «Hello, World! N» есть уязвимая_функция, проверьте эту функцию после ввода Видно, что только что появившийся странный адрес является пе.

Установка и развертывание Kubernetes

На самом деле, я опубликовал статью в этом разделе давным -давно, но она не достаточно подробно, и уровень не является ясным. Когда я развернулся сегодня, я увидел его достаточно (хотя это было успешн.

На стороне многопроцессорного сервера — (2) *

Обработка сигнала Родительский процесс часто очень занят, поэтому вы не можете просто вызвать функцию waitpid, чтобы дождаться завершения дочернего процесса. Затем обсудите решение. Обратитесь .

Вам также может понравиться

C#Личные заметки

1. Метод расширения: добавьте статический перед именем класса, добавьте это перед параметра метода, например: расширить класс строки public static class string < Public static .

[Springcould] Код сервисного шлюза (Zuul)

1. Подготовка Проект в предыдущем учебном пособии хорошо построен [Springcould] открытие фактического боя [Springcould] Регистрация и обнаружение сервера Eureka Eureka [Springcould] Служба Производите.

Решите проблему, что координаты и значения данных с несколькими скидками для echarts не совпадают

При наличии нескольких дисконтированных данных echarts может сконфигурировать значение стека для использования суммированного значения или одного значения.

Список () и кортеж () Методы в Python

Многие люди будут думать о следующих способах генерировать список: Будет построить такой [«A», «B», «C», «D»] на самом деле ошибка Yuan Group также тако.

Источник

HP ProLiant DL360 Gen9 — Memory initialization error

Продолжение эпопеи с ошибками памяти на сервере HP ProLiant DL360 Gen9. Только что вернулся из ЦОД, задача по расширению памяти сервера всё ещё не выполнена.

Напоминаю, что в старый сервер HP ProLiant DL360 Gen9 было дополнительно воткнуто 8 планок DIMM по 16 ГБ каждая. После этого мы словили ошибку и вычислили сбойную память в 10 слоте второго процессора.

Сервер отключил битую планку памяти, и ещё две вместе с ней, которые висели на том же канале. Ясно было, что планку нужно менять. Поскольку мы планировали расширять память на нескольких серверах, то памяти купили много, запасные планки есть. Вот я и поехал, а перед поездкой взял с собой все новые планки, чтобы их тоже проверить. А если вся партия битая, возможно, там ещё есть нерабочие планки? Редкость, конечно. Но беру всё.

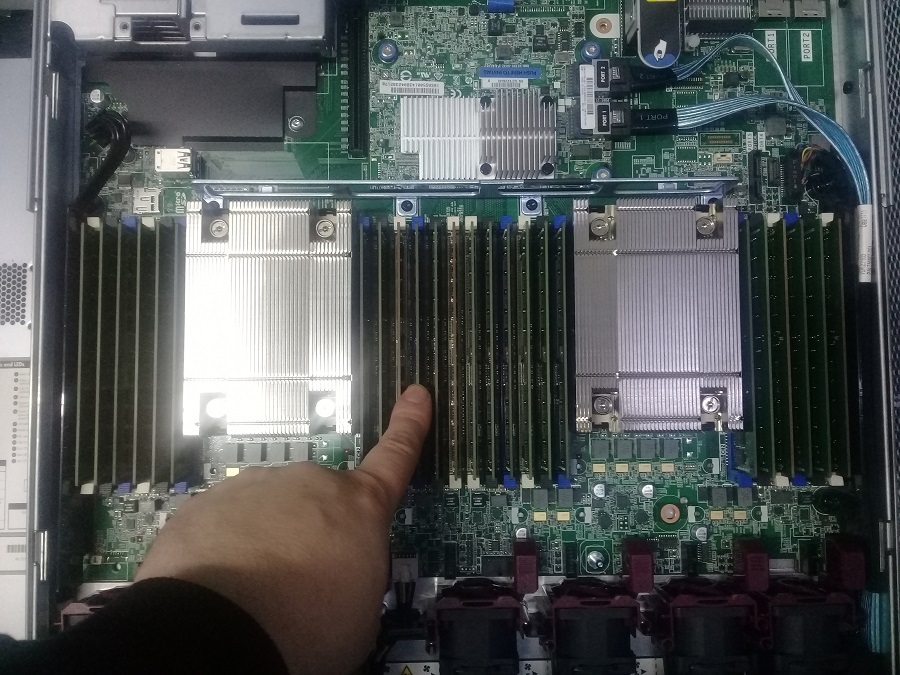

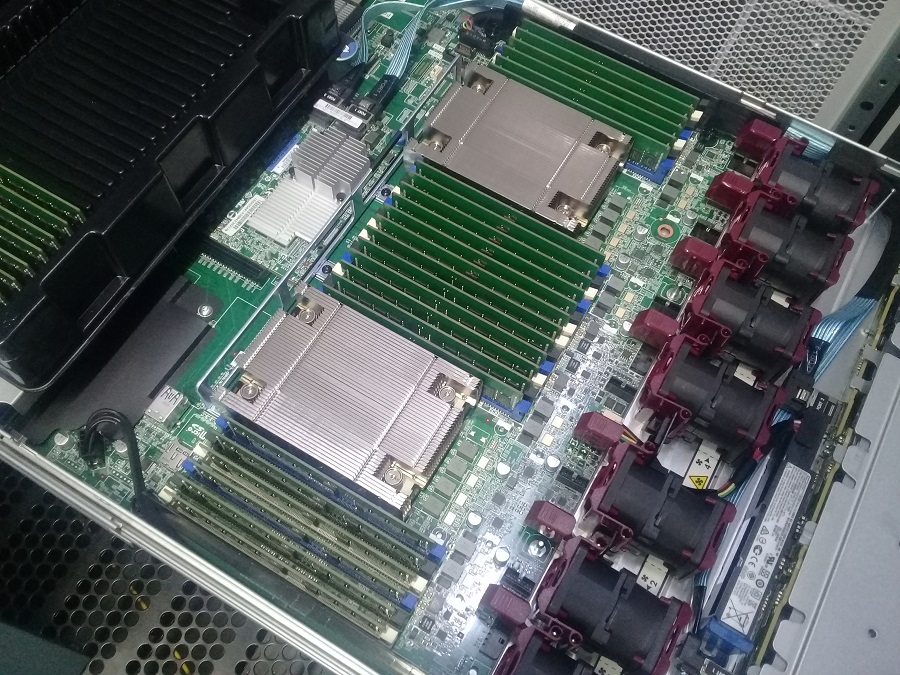

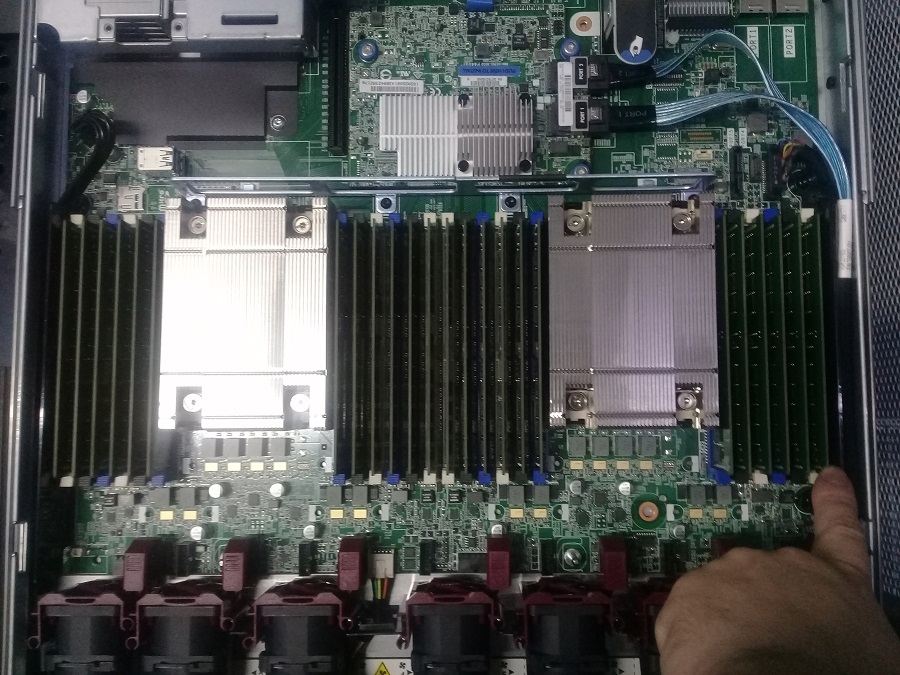

Дубль два

Приезжаю в ЦОД, открываю сервер. Нахожу десятый слот второго процессора, благо все слоты подписаны на материнке. И на крышке схема есть.

Битую планку извлекаю, сразу наклеиваю на неё наклейку и помечаю DEF — defective. Вместо неё ставлю новую планку. Затем извлекаю все 16 планок, которые в сервере стояли изначально. Они явно рабочие, откладываю в сторонку.

Все пустые слоты забиваю новыми планками. Нужно же мне проверить эту партию.

Вся память не влезла. Нужно будет потом её тоже проверить. Собираем сервер обратно и включаем.

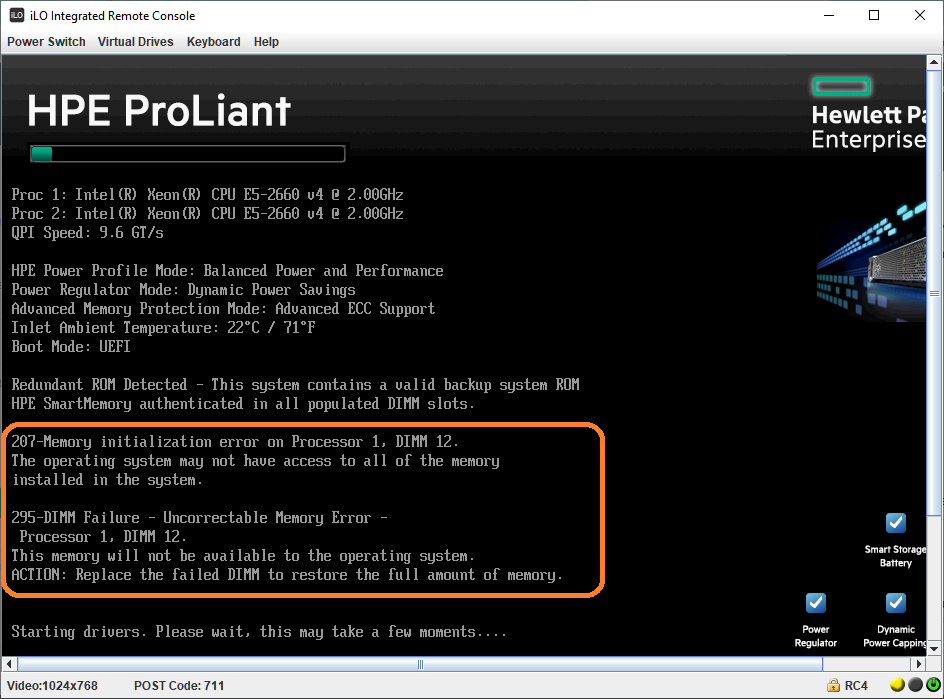

EVENT (30 Sep 13:21): POST Error: 207-Memory initialization error on Processor 1, DIMM 12. The operating system may not have access to all of the memory installed in the system.

EVENT (30 Sep 16:21): POST Error: 295-DIMM Failure — Uncorrectable Memory Error — Processor 1, DIMM 12. This memory will not be available to the operating system. ACTION: Replace the failed DIMM to restore the full amount of memory.

Теперь уже первый процессор, 12 слот.

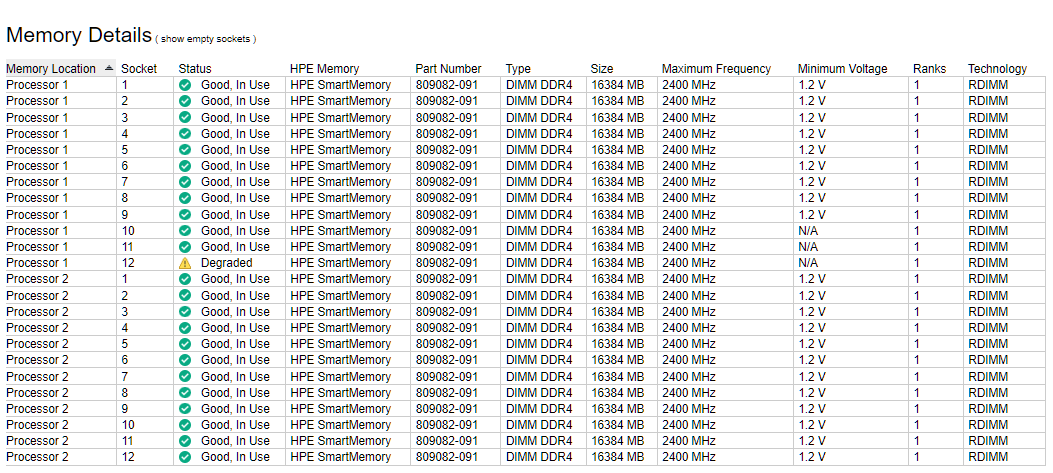

Вот так бывает. В закупленной партии уже две битые планки. Ошибка точно такая же. Сервер также отключил битую планку и две на том же канале. Зато на втором процессоре теперь полный рабочий комплект.

Извлекаю вторую битую планку, меняю на новую.

В итоге я не поленился, проверил все планки, которые взял с собой. К счастью, в партии оказалось только две неисправных планки памяти. Но это не точно. Потому что в первый раз сервер тоже показал что всё нормально, а потом память отвалилась под нагрузкой.

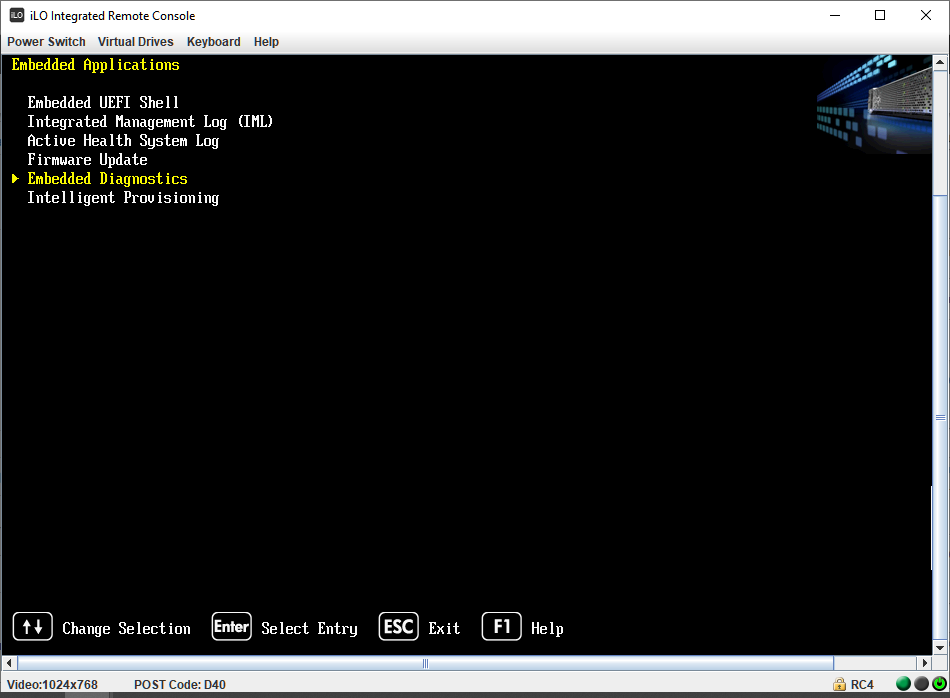

Запускаю встроенную диагностическую утилиту.

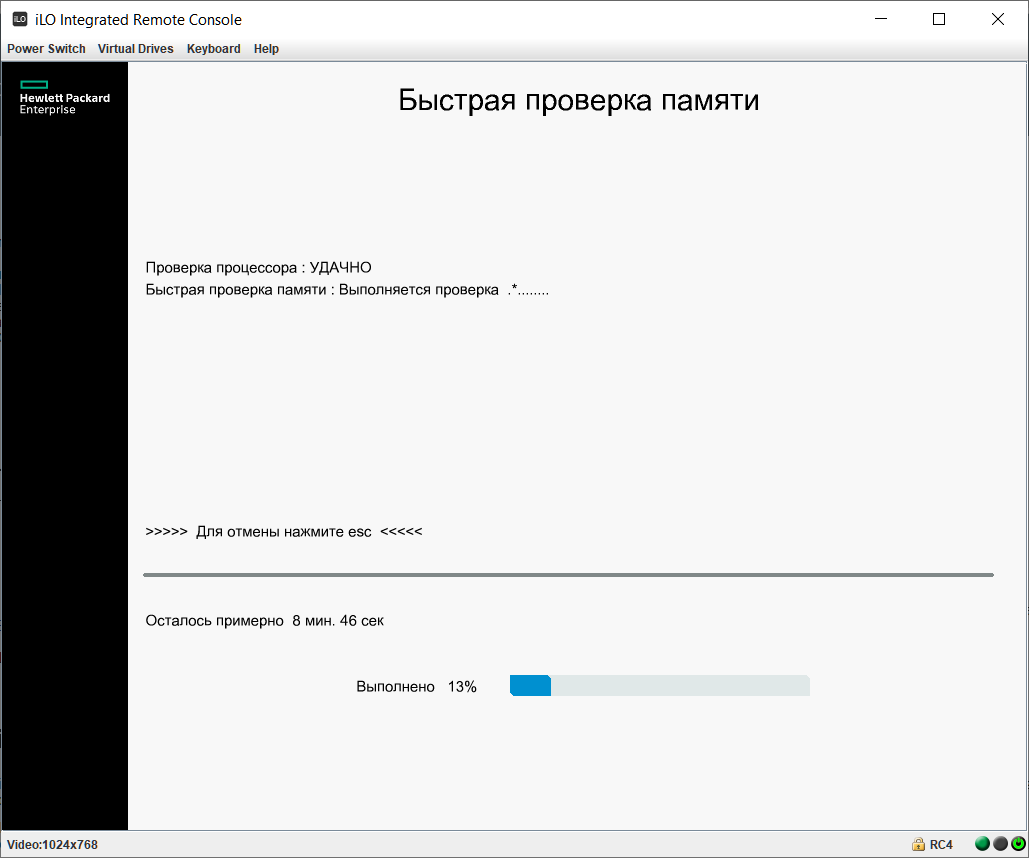

Запускаю мгновенную проверку памяти.

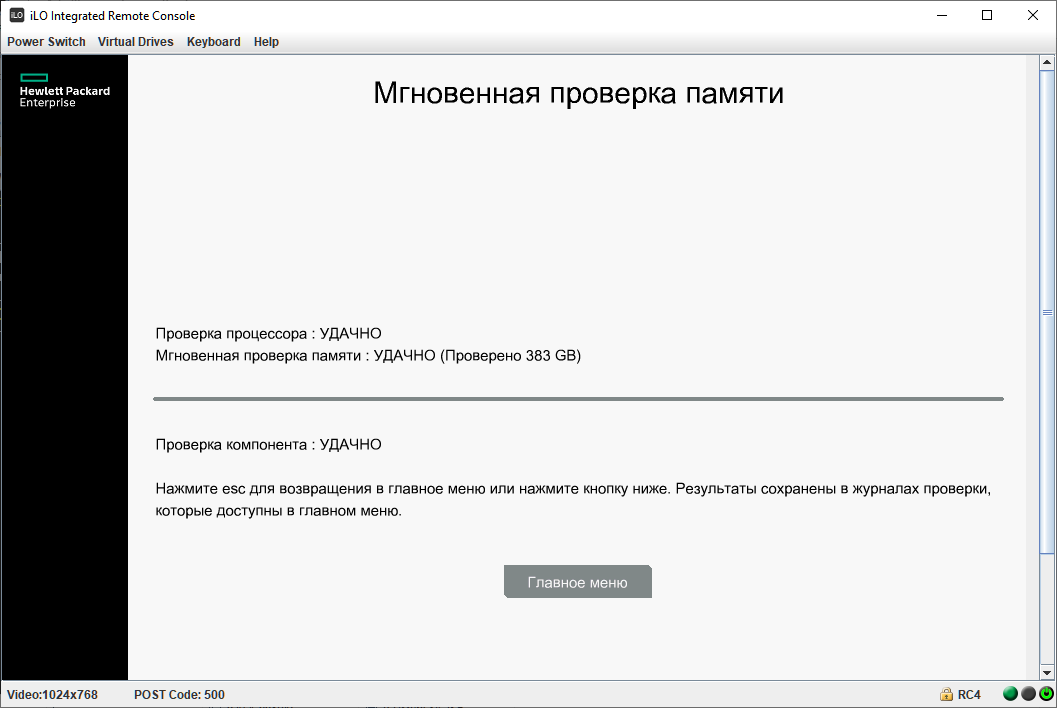

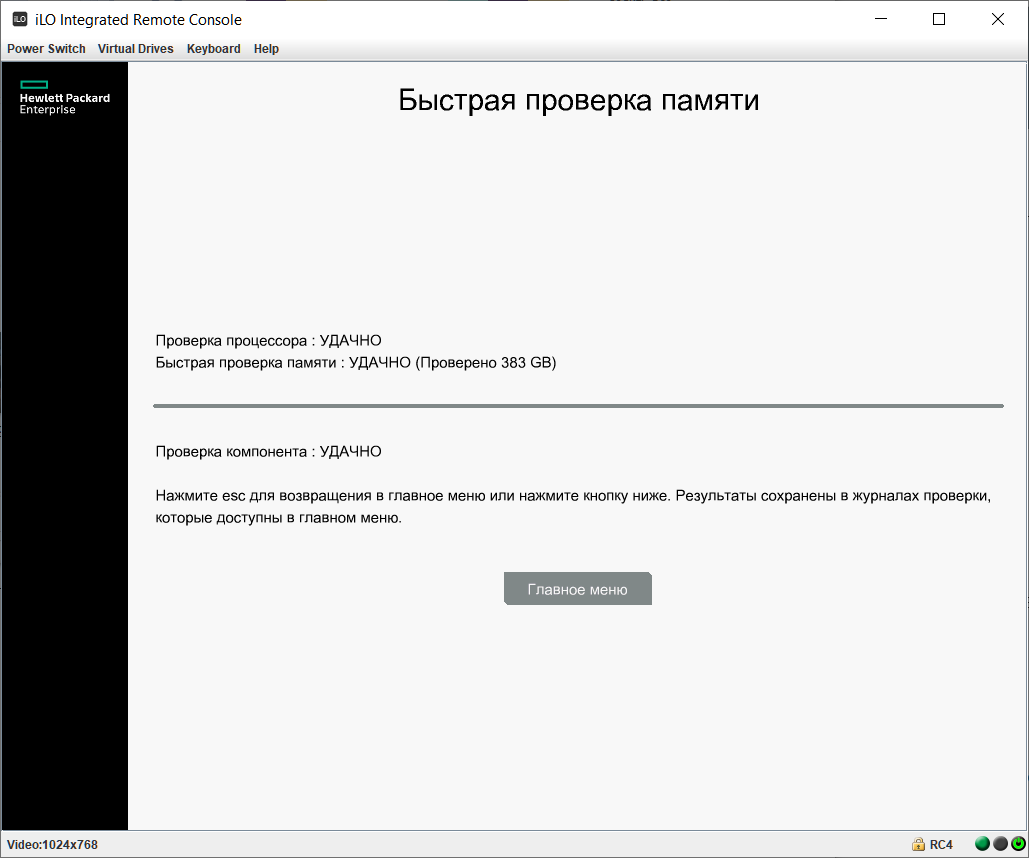

Утилита пишет, что мгновенная проверка памяти выполняется за 3 минуты, не верьте ей. У меня ушло минут 15. В итоге: Мгновенная проверка памяти: УДАЧНО. Проверено 383 Гб. Всё в норме.

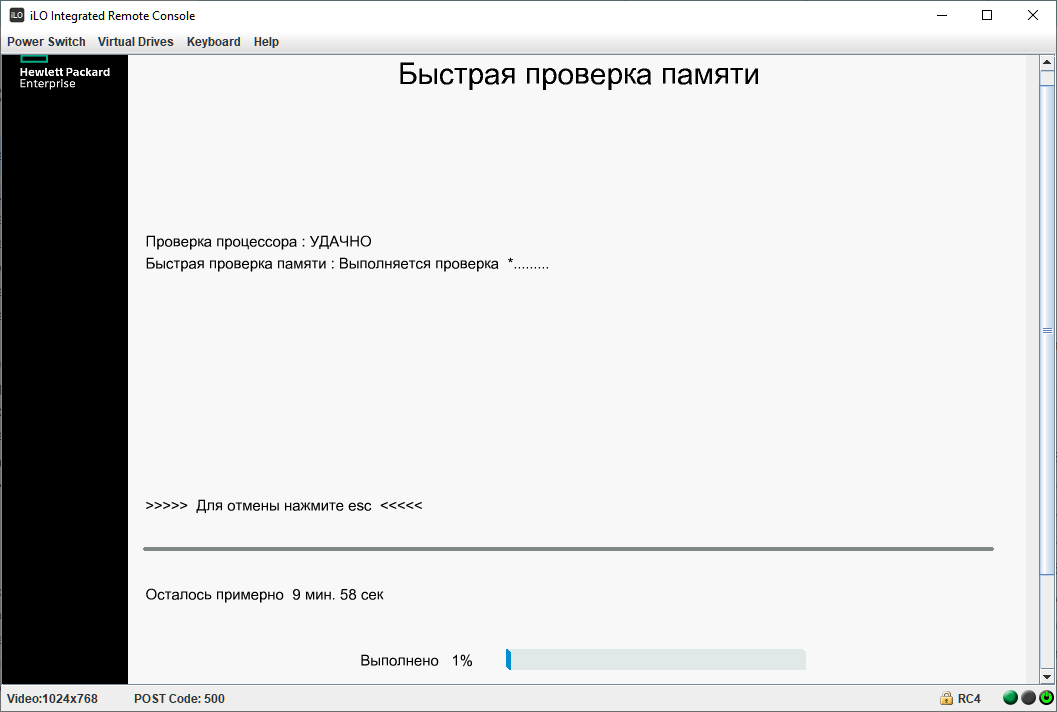

Перед уходом запускаю быструю проверку памяти.

Утилита пишет, что быстрая проверка памяти выполняется за 10 минут, не верьте ей. Прошло два с половиной часа.

Выполнено 13%. Если прикинуть, то быстрая проверка займёт 1154 минуты. Сутки. А ведь есть ещё полная проверка, не стану её запускать. Оставляю утилиту работать, завтра попытаюсь запустить сервер в бой, если память не накроется.

Если у вас есть возможность проверить закупленное оборудование, то сделайте это.

Быстрая проверка памяти: УДАЧНО. Проверено 383 Гб. Всё в норме.

Источник